この記事の要約

- 米研究チームが新型3Dチップを開発

- 商用プロセスでの製造に世界初成功

- AI処理性能が従来の約4倍に向上

2025年12月28日、スタンフォード大学やMITなどの共同研究チームが、従来の半導体技術の限界を打ち破る「モノリシック3Dチップ」の開発を発表しました。この技術は、計算を行うプロセッサとデータを記憶するメモリを垂直方向に積み重ねることで、AI技術の課題であるデータ転送の遅延を解消するものです。特筆すべきは、これが実験室レベルではなく、米国の商用ファウンドリで製造された点にあります。IT業界やプログラミング、ソフトウェア開発の現場に大きなインパクトを与えるこのニュースは、将来的にエネルギー効率を最大1000倍改善する可能性を秘めています。

開発の背景と製造プロセス

スタンフォード大学、MIT(マサチューセッツ工科大学)、カーネギーメロン大学、ペンシルベニア大学の研究チームは、米国の半導体ファウンドリであるSkyWater Technologyの商用プロセスを使用し、モノリシック3Dチップの製造に成功しました。これは、既存の商用設備を用いて高密度な3D集積回路を作製した世界初の事例となります。

これまでの3Dチップ研究は実験室内の特殊な環境に限られていましたが、今回の成果は「既存の工場で作れる」ことを証明した点に大きな意義があります。つまり、この高性能なAI技術向けハードウェアが、将来的に低コストかつ大量に市場へ供給される道が開かれたことを意味します。

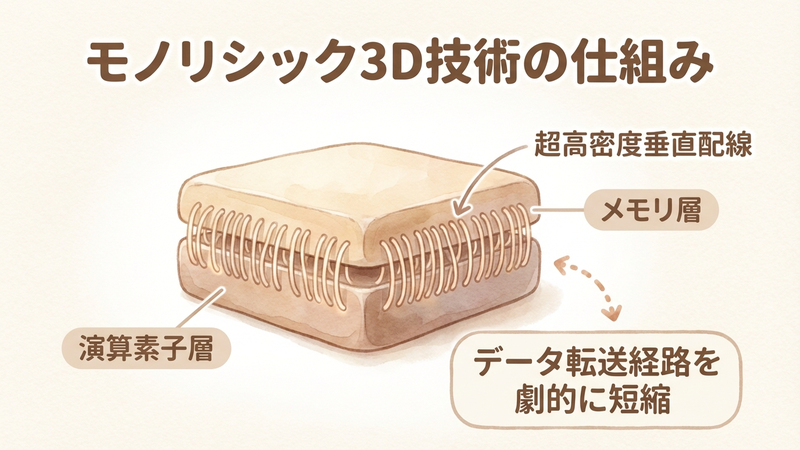

モノリシック3D技術の仕組み

開発されたチップは、演算素子とメモリ層を別々に製造して張り合わせるのではなく、単一のチップ上に層として構築する「モノリシック(一体型)」構造を採用しています。これにより、層間をつなぐ垂直配線を超高密度に配置することが可能となり、従来のチップ構造と比較してデータ転送経路を劇的に短縮しました。

これは、平屋建ての建物を高層ビルに建て替えるようなイメージです。各部屋(素子)への移動距離(配線)が圧倒的に短くなるため、データの移動にかかる時間とエネルギーを大幅に削減できます。高度なソフトウェア処理を支える基盤として、物理的な構造改革が行われたと言えます。

AI処理性能と効率の飛躍的向上

初期のテスト結果において、この新型3Dチップは従来の2Dチップと比較して、AI処理のスループット(単位時間あたりの処理能力)が約4倍に向上したことが記録されました。さらに研究チームは、将来的にエネルギー遅延積(EDP)を最大で1000倍改善できる可能性があると試算しています。

現状ですぐに4倍の高速化が得られるだけでなく、将来的には桁違いの省エネ性能が期待されています。これにより、膨大な電力を消費する大規模なAIモデルの学習や推論が、より少ないエネルギーで実行可能になり、ITインフラの持続可能性に大きく貢献することが予想されます。

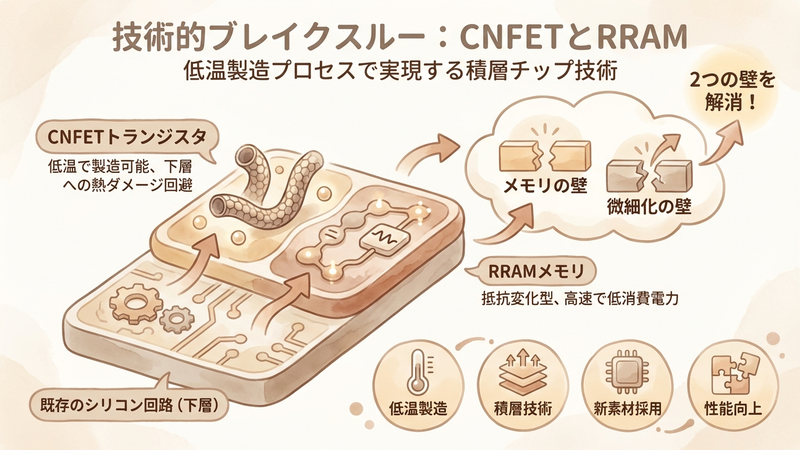

技術的ブレイクスルー:CNFETとRRAM

このチップの実現には、シリコンの代わりに低温で製造可能なカーボンナノチューブトランジスタ(CNFET)と、メモリ技術としてRRAM(抵抗変化型メモリ)が採用されました。これにより、下の層にある回路を熱で損傷させることなく、上層に新しい回路を構築することが可能になり、「メモリの壁」と「微細化の壁」の解消に寄与しています。

従来のシリコン素材は製造に高温が必要なため、積み上げることが困難でした。新素材の採用によりその熱問題をクリアし、メモリとプロセッサを極限まで近づけることに成功しました。これはハードウェアの制約に縛られていた開発ツールやアルゴリズムの設計思想にも、新たな自由度をもたらす技術革新です。

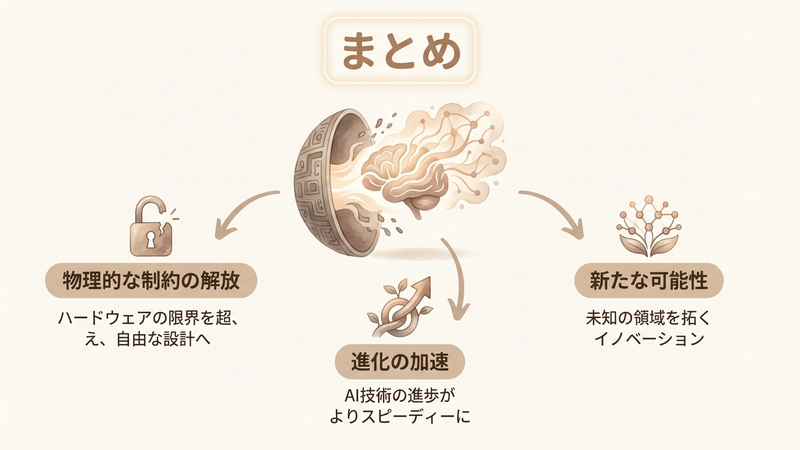

まとめ

今回のニュースは、AI技術の進化においてハードウェアの物理的な制約が取り払われつつあることを示しています。ポイントは以下の通りです。

- スタンフォード大学らが、商用ラインで製造可能なモノリシック3Dチップを開発しました。

- 新素材CNFETの活用により、従来の2Dチップ比で約4倍の性能向上を実現しています。

- 長年の課題であった「メモリの壁」を解消し、将来的には1000倍の効率化が見込まれます。

この技術が実用化されれば、プログラミングやソフトウェア開発の現場において、より高度なAI処理を低遅延・低消費電力で実装できるようになります。今後の量産化プロセスと、大手テック企業による採用動向が注目されます。

本記事は生成AIにより複数の公開情報を元に自動生成されています。重要な判断の際は、複数の情報源を参照されることを推奨します。 詳細は免責事項をご確認ください。